# 16-Channel PWM Constant Current LED Driver for 1:8 Time-Multiplexing Applications

#### **Features**

- 3.0V-5.5V supply voltage

- 16 constant current output channels

- Constant output current range:

- 2~45mA @ 5V supply voltage

- 2~30mA @ 3.3V supply voltage

- Excellent output current accuracy:

Between channels:: <±2.5% (Max.)

Between ICs: <±3%(Max.)

- Built-in 4K-bit SRAM to support time-multiplexing for 1 ~ 8 scans

- 16/15/14/13-bit color depth PWM control to improve visual refresh rate

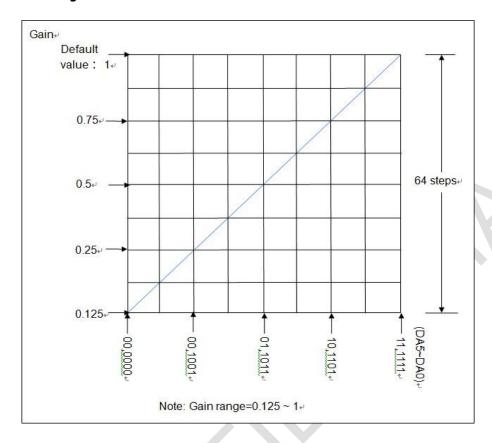

- 6-bit current gain, 12.5%~100%

- LED failure isolation

- -LED failure induced cross elimination

- LED open detection

- Integrating ghost elimination circuit

- Intelligent power saving modes

- Dynamic power saving (when all frame data is zero)

- Dynamic+ power saving (when displaying dynamic video with various brightness)

- GCLK multiplier technology

- Maximum DCLK frequency: 30MHz

### **Product Description**

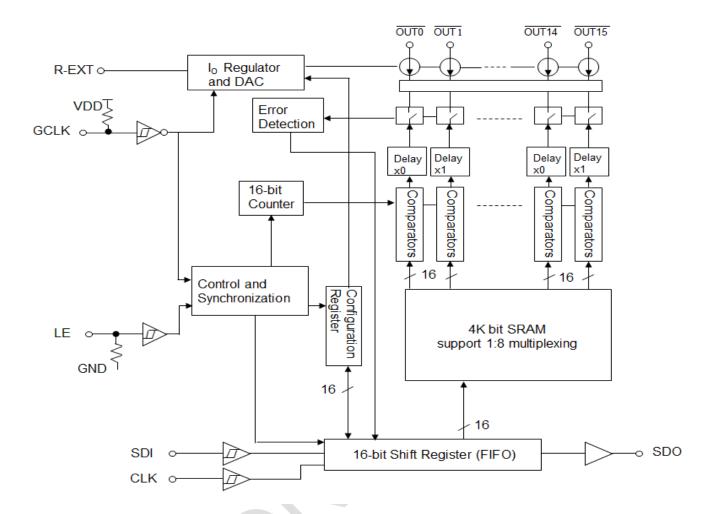

MBI5251 is designed for LED video applications using internal Pulse Width Modulation (PWM) control with selectable 16/15/14/13-bit color depth. MBI5251 features a 16-bit shift register which converts serial input data into each pixel's gray scale of the output port. Sixteen regulated current ports are designed to provide uniform and constant current sinks for driving LEDs with a wide range of V<sub>F</sub> variations. The output current can be preset through an external resistor. The innovative architecture with embedded SRAM is designed to support up to 1:8 time-multiplexing applications. Users only need to send the whole frame data once and to store in the embedded SRAM of the LED driver, instead of sending every time when the scan line is changed. It helps to save the data bandwidth and to achieve high grayscale with very low data clock rate. With scan-type Scrambled-PWM (S-PWM) technology, MBI5251 enhances PWM by scrambling the "on" time of each scan line into several "on" periods and sequentially drives each scan line for a short "on" period. The enhancement equivalently increases the visual refresh rate of scan-type LED displays. In addition, the innovative GCLK multiplier technique doubles visual refresh rate.

MBI5251 drives the corresponding LEDs to the brightness specified by image data. With MBI5251, all output channels can be built with 16-bit color depth (65,536 gray scales). When building a 16-bit color depth video, S-PWM technology reduces the flickers and improves the image fidelity.

Through compulsory error detection, MBI5251 detects individual LED for open-circuit errors without extra

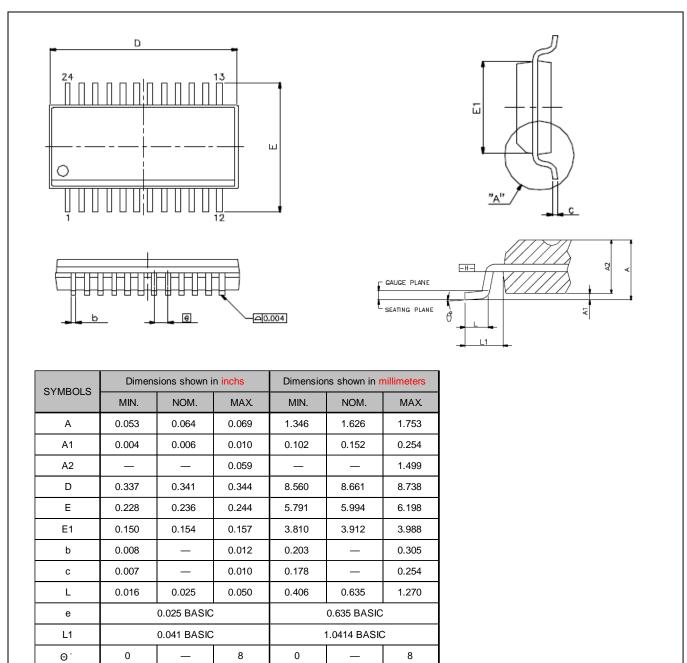

Shrink SOP

components. MBI5251 equipped an innovative cross elimination function, and it solves the cross phenomenon induced by failure LEDs. Besides, integrated ghost elimination circuit eases the ghost problems.

### **Block Diagram**

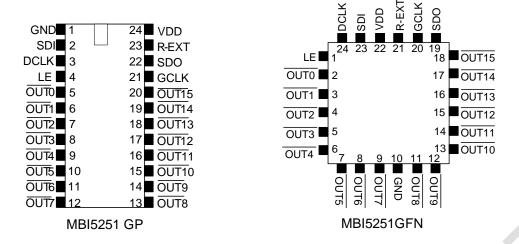

### **Pin Configuration**

**Terminal Description**

| Pin Name     | Function                                                                                                                              |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| GND          | Ground terminal for control logic and current sink                                                                                    |

| SDI          | Serial-data input to the shift register                                                                                               |

| DCLK         | Clock input terminal used to shift data on rising edge and carries command information when LE is asserted.                           |

| LE           | Data strobe terminal and controlling command with DCLK                                                                                |

| OUTO ~ OUT15 | Constant current output terminals                                                                                                     |

| GCLK         | Gray scale clock terminal Clock input for gray scale. The gray scale display is counted by gray scale clock compared with input data. |

| SDO          | Serial-data output to the receiver-end SDI of next LED driver                                                                         |

| R-EXT        | Input terminal used to connect an external resistor for setting up output current for all output channels                             |

| VDD          | 3.3V/5V supply voltage terminal                                                                                                       |

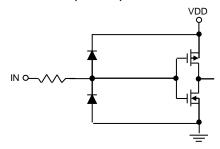

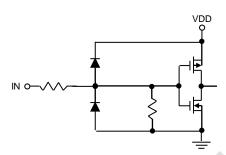

### **Equivalent Circuits of Inputs and Outputs**

**GCLK, DCLK, SDI terminal**

**LE Terminal**

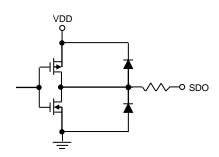

#### **SDO Terminal**

### **Maximum Rating**

| Charac                       | eteristic                                          | Symbol              | Rating                    | Unit |

|------------------------------|----------------------------------------------------|---------------------|---------------------------|------|

| Supply Voltage               |                                                    | V <sub>DD</sub>     | 0~5.5                     | V    |

| Input Pin Voltage (SDI, DCLK | , GCLK, LE)                                        | V <sub>IN</sub>     | -0.4~V <sub>DD</sub> +0.4 | V    |

| Sustaining Voltage at OUT Po | ort                                                | V <sub>DS</sub>     | -0.5~7                    | V    |

| Output Current               |                                                    | Іоит                | +45                       | mA   |

| GND Terminal Current         |                                                    | I <sub>GND</sub>    | 360                       | mA   |

| Power Dissipation            | GP Type                                            |                     | TBD                       | 10/  |

| (On 4 Layer PCB, Ta=25°C)*   | GFN Type                                           | P <sub>D</sub>      | TBD                       | W    |

| Thermal Resistance           | GP Type                                            | D                   | TBD                       | °C/W |

| (On 4 Layer PCB, Ta=25°C)*   | GFN Type                                           | $R_{th(j-a)}$       | TBD                       | C/VV |

| Junction Temperature         |                                                    | T <sub>j</sub> ,max | 150**                     | °C   |

| Operating Ambient Temperatu  | ıre                                                | Topr                | -40~+85                   | °C   |

| Storage Temperature          |                                                    | T <sub>stg</sub>    | -55~+150                  | °C   |

| ESD Rating                   | Human Body Mode<br>(MIL-STD-883H Method<br>3015.8) | НВМ                 | TBD                       | -    |

|                              | Machine Mode<br>(ANSI/ ESD S5.2-2009)              | MM                  | TBD                       | -    |

<sup>\*</sup>The PCB size is 76.2mm\*114.3mm in simulation. Please refer to JEDEC JESD51.

Note: The performance of thermal dissipation is strongly related to the size of thermal pad, thickness and layer numbers of the PCB. The empirical thermal resistance may be different from simulative value. User should plan for expected thermal dissipation performance by selecting package and arranging layout of the PCB to maximize the capability.

<sup>\*\*</sup>Operation at the maximum rating for extended periods may reduce the device reliability; therefore, the suggested junction temperature of the device is under 125°C.

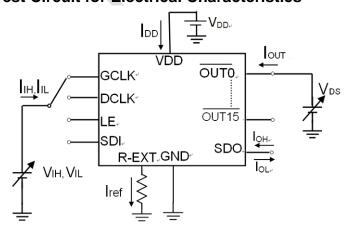

Electrical Characteristics (V<sub>DD</sub>=5.0V, Ta=25°C)

|                        | Characteris                 | tics               | Symbol                                         | Condition                                      | on                      | Min.                | Тур. | Max.                | Unit  |

|------------------------|-----------------------------|--------------------|------------------------------------------------|------------------------------------------------|-------------------------|---------------------|------|---------------------|-------|

| Supply '               | Voltage                     |                    | $V_{DD}$                                       | -                                              |                         | 4.5                 | 5.0  | 5.5                 | V     |

| Sustaini               | ing Voltage a               | t OUT Ports        | V <sub>DS</sub>                                | OUT0 ~ OUT15                                   |                         | -                   | -    | 7.0                 | V     |

|                        |                             |                    | Гоит                                           | Refer to "Test Circuit Characteristics"        | t for Electrical        | 2                   | -    | 45                  | mA    |

| Output (               | Current                     |                    | Іон                                            | SDO                                            |                         | -                   | -    | -1.0                | mΑ    |

|                        |                             |                    | loL                                            | SDO                                            | -                       | -                   | 1.0  | mA                  |       |

| I                      | alta sia                    | "H" level          | Vін                                            | Ta=-40~85°C                                    |                         | 0.7xV <sub>DD</sub> | -    | V <sub>DD</sub>     | V     |

| Input Vo               | oitage                      | "L" level          | VIL                                            | Ta=-40~85°C                                    |                         | GND                 |      | 0.3xV <sub>DD</sub> | V     |

| Output I               | Leakage Curr                | ent                | Іон                                            | V <sub>DS</sub> =17.0V                         |                         |                     | -    | 0.5                 | μA    |

| 0 . 1 1 )              | /-It                        | 000                | Vон                                            | I <sub>OH</sub> =-1.0mA                        | 4.6                     | -                   | -    | V                   |       |

| Output Voltage SDO     |                             | SDO                | V <sub>OL</sub>                                | I <sub>OL</sub> =+1.0mA                        |                         | -                   | -    | 0.4                 | V     |

| Current Skew (Channel) |                             | dl <sub>OUT1</sub> | I <sub>OUT</sub> =2mA<br>V <sub>DS</sub> =1.0V | R <sub>ext</sub> =7.2KΩ                        | -                       | ±1.5                | ±2.5 | %                   |       |

| Current                | Skew (IC)                   |                    | dl <sub>OUT2</sub>                             | I <sub>OUT</sub> =2mA<br>V <sub>DS</sub> =1.0V | R <sub>ext</sub> =7.2KΩ | -                   | ±1.5 | ±3.0                | %     |

| Output '               | Current vs.<br>Voltage Regu | lation*            | %/dV <sub>DS</sub>                             | V <sub>DS</sub> within 1.0V and 3.0V           |                         | -                   | ±0.1 | ±0.5                | %/V   |

|                        | Current vs.<br>Voltage Regu | ılation*           | %/dV <sub>DD</sub>                             | V <sub>DD</sub> within 4.5V and                | 5.5V                    | -                   | ±1.0 | ±2.0                | % / V |

| LED Op                 | en Detection                | Threshold          | V <sub>OD,ТН</sub>                             | default                                        |                         | -                   | 0.5  | -                   | V     |

| Pull-dov               | vn Resistor                 |                    | R <sub>IN</sub> (down)                         | LE                                             |                         | 250                 | 450  | 800                 | ΚΩ    |

|                        | "Off"                       |                    | I <sub>DD</sub> (off) 1                        | R <sub>ext</sub> =Open, OUT0 ~                 | OUT15 =Off              | -                   | 10.2 |                     |       |

|                        | (SDI=DCLK=<br>=0Hz)         | =GCLK              | I <sub>DD</sub> (off) 2                        | $R_{ext}=7.2K\Omega$ , $\overline{OUT0}$ ~     | ~ OUT15 =Off            | -                   | 12.2 |                     |       |

| Supply<br>Current      | ,                           |                    | I <sub>DD</sub> (off) 3                        | R <sub>ext</sub> =360Ω, OUT0 ~                 | OUT15 =Off              | -                   | 14.2 |                     | mA    |

|                        | "On"                        |                    | I <sub>DD</sub> (on) 2                         | $R_{ext}=7.2K\Omega$ , $\overline{OUT0}$ ~     | - OUT15 =On             | -                   | 12.2 |                     |       |

|                        | (GCLK=20M                   | Hz)                | I <sub>DD</sub> (on) 3                         | R <sub>ext</sub> =320Ω, <del>OUT0</del> ~      | OUT15 =On               | -                   | 14.2 |                     |       |

<sup>\*</sup>One channel on.

# Electrical Characteristics (V<sub>DD</sub>=3.3V, Ta=25°C)

|                        | Characteris                | stics              | Symbol                                           | Cond                                             | dition                  | Min.         | Тур. | Max.         | Unit |

|------------------------|----------------------------|--------------------|--------------------------------------------------|--------------------------------------------------|-------------------------|--------------|------|--------------|------|

| Supply                 | Voltage                    |                    | $V_{DD}$                                         |                                                  | -                       | 3.0          | 3.3  | 3.6          | V    |

| Sustain                | ing Voltage a              | at OUT Ports       | V <sub>DS</sub>                                  | OUT0 ~ OUT15                                     | -                       | -            | -    | 7.0          | V    |

|                        |                            |                    | Гоит                                             | Refer to "Test Cir Characteristics"              | cuit for Electrical     | 2            | 1    | 30           | mA   |

| Output                 | Current                    |                    | Іон                                              | SDO                                              |                         | -            | -    | -1.0         | mΑ   |

|                        |                            |                    | loL                                              | SDO                                              |                         | -            | -    | 1.0          | mΑ   |

| I                      | -14                        | "H" level          | V <sub>IH</sub>                                  | Ta=-40~85°C                                      |                         | $0.7xV_{DD}$ | -    | $V_{DD}$     | V    |

| Input Vo               | oitage                     | "L" level          | V <sub>IL</sub>                                  | Ta=-40~85°C                                      |                         | GND          | -    | $0.3xV_{DD}$ | V    |

| Output                 | Leakage Cui                | rent               | I <sub>OH</sub>                                  | V <sub>DS</sub> =17.0V                           |                         | -            | -    | 0.5          | μA   |

| 0.4                    | \                          | 000                | Vон                                              | I <sub>OH</sub> =-1.0mA                          | 2.9                     | -            | -    | V            |      |

| Output Voltage SDO     |                            | SDO                | VoL                                              | I <sub>OL</sub> =+1.0mA                          | -                       | -            | 0.4  | V            |      |

| Current Skew (Channel) |                            | dl <sub>OUT1</sub> | I <sub>OUT</sub> =0.5mA<br>V <sub>DS</sub> =1.0V | R <sub>ext</sub> =7.2KΩ                          |                         | ±1.5         | ±2.5 | %            |      |

| Current                | Skew (IC)                  |                    | dl <sub>OUT2</sub>                               | I <sub>OUT</sub> =0.5mA<br>V <sub>DS</sub> =1.0V | R <sub>ext</sub> =7.2KΩ | -            | ±1.5 | ±3.0         | %    |

|                        | Current vs.<br>Voltage Reg | ulation*           | %/dV <sub>DS</sub>                               | V <sub>DS</sub> within 1.0V and 3.0V             |                         | -            | ±0.1 | ±0.3         | %/V  |

|                        | Current vs.<br>Voltage Reg | ulation*           | %/dV <sub>DD</sub>                               | V <sub>DD</sub> within 3.0V a                    | nd 3.6V                 | -            | ±1.0 | ±2.0         | %/V  |

| LED Op                 | en Detection               | n Threshold        | $V_{\text{OD,TH}}$                               | default                                          |                         | -            | 0.5  | -            | V    |

| Pull-dov               | wn Resistor                |                    | R <sub>IN</sub> (down)                           | LE                                               |                         | 250          | 450  | 800          | ΚΩ   |

|                        |                            |                    | I <sub>DD</sub> (off) 1                          | R <sub>ext</sub> =Open, OUTO                     | OUT15 =Off              | -            | 9.7  |              |      |

|                        | "Off"<br>(SDI=DCLK         | =GCLK=0Hz)         | I <sub>DD</sub> (off) 2                          | R <sub>ext</sub> =7.2KΩ, OUT                     | 0 ~ OUT15 =Off          | -            | 11.7 |              | ^    |

| Supply<br>Current      | `                          | 302. ( 0.12)       | I <sub>DD</sub> (off) 3                          | R <sub>ext</sub> =320Ω, OUTO                     | 0 ~ OUT15 =Off          |              | 13.7 |              | mA   |

|                        | "On"                       |                    | I <sub>DD</sub> (on) 2                           | R <sub>ext</sub> =7.2KΩ, OUT                     |                         | -            | 7.4  |              |      |

|                        | (GCLK=20N                  | MHz)               | I <sub>DD</sub> (on) 3                           | R <sub>ext</sub> =320Ω, OUTO                     | OUT15 =On               |              | 13.7 |              |      |

<sup>\*</sup>One channel on.

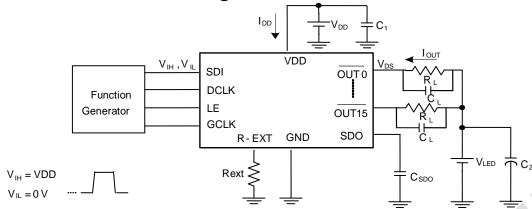

#### **Test Circuit for Electrical Characteristics**

Figure 2

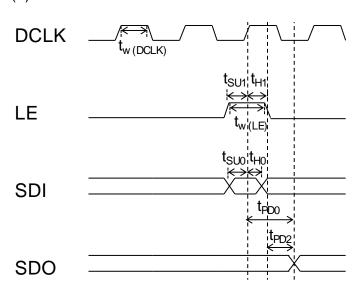

Switching Characteristics (V<sub>DD</sub>=5.0V, Ta=25°C)

| Characteristics                                |                     | Symbol                       | Condition                                        | Min. | Тур. | Max. | Unit |

|------------------------------------------------|---------------------|------------------------------|--------------------------------------------------|------|------|------|------|

|                                                | SDI - DCLK ↑        | t <sub>SU0</sub>             |                                                  | 5    | -    | -    | ns   |

| Out on The c                                   | LE↑ - DCLK↑         | t <sub>SU1</sub>             |                                                  | 8    | -    | -    | ns   |

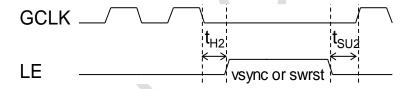

| Setup Time                                     | LE ↓ (Vsync) – GCLK | t <sub>SU2</sub>             |                                                  | 1200 | -    | -    | ns   |

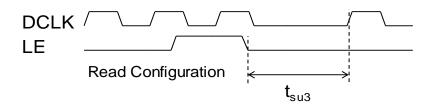

|                                                | LE↓ - DCLK↑         | t <sub>SU3</sub>             |                                                  | 50   | -    | -    | ns   |

|                                                | DCLK↑ - SDI         | t <sub>H0</sub>              |                                                  | 6    | -    | -    | ns   |

| Hold Time                                      | DCLK↑ - LE          | t <sub>H1</sub>              |                                                  | 8    | -    | -    | ns   |

|                                                | GCLK – LE ↑ (Vsync) | t <sub>H2</sub>              |                                                  | 300  | -    | -    | ns   |

|                                                | DCLK - SDO          | t <sub>PD0</sub>             |                                                  | -    | 22   | 25   | ns   |

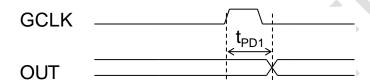

| Propagation Delay<br>Time                      | GCLK - OUT2n **     | t <sub>PD1</sub>             | $V_{DD}$ =5.0 $V_{IH}$ = $V_{DD}$                | -    | 35   | -    | ns   |

| Time                                           | LE – SDO            |                              | VIH= V DD<br>VIL=GND                             |      | 30   | 40   | ns   |

| Pulse Width                                    |                     |                              | $R_{ext}=1.4K\Omega$<br>$V_{DS}=1V$              | 15   | -    | -    | ns   |

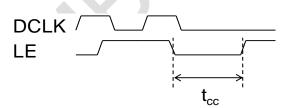

| Command to Comman                              | d                   | Тсс                          | R <sub>L</sub> =300Ω                             | 50   | -    | -    | ns   |

| Data Clock Frequency                           |                     | F <sub>DCLK</sub>            | C <sub>L</sub> =10pF<br>C <sub>1</sub> =100nF    | -    | -    | 30   | MHz  |

| Gray Scale Clock Freq                          | uency***            | FGCLK                        | C <sub>2</sub> =10µF                             | -    | -    | 33   | MHz  |

| GCLK frequency (when GCLK multiplier           | is enabled)         | FGCLK                        | C <sub>SDO</sub> =10pF<br>V <sub>LED</sub> =4.0V | -    | -    | 16.6 | MHz  |

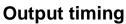

| Min Clock(GCLK/ DCL                            | K) Pulse Width****  | t <sub>W(CLK)</sub>          |                                                  | 12   | -    | -    | ns   |

| Ratio of (GCLK freq)/ (                        | DCLK freq)          | R <sub>(GCLK/DCL</sub><br>K) |                                                  | 20   | -    | -    | %    |

| Compulsory Error Detection Operation time***** |                     | terr-c                       |                                                  | 700  | -    | -    | ns   |

| Output Rise Time of O                          | utput Ports         | toR                          |                                                  | -    | 15   | 20   | ns   |

| Output Fall Time of Ou                         | tput Ports          | t <sub>OF</sub>              |                                                  | -    | 15   | 20   | ns   |

| Output Rise Time of O                          | utput Ports (Slow)  | t <sub>OR</sub>              |                                                  |      | 30   | 40   | ns   |

| Output Fall Time of Ou                         | tput Ports (Slow)   | tof                          |                                                  |      | 30   | 40   | ns   |

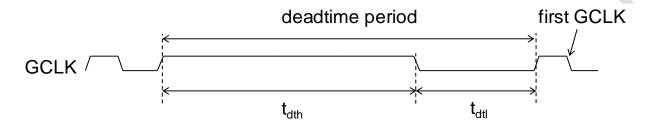

| Dead Time                                      |                     | t <sub>dth</sub>             |                                                  | 300  | -    | -    | ns   |

| Dead Time (Low state)                          |                     | t <sub>dtl</sub>             |                                                  | 1200 | -    | -    | ns   |

<sup>\*</sup>Output waveforms have good uniformity among channels.

<sup>\*\*</sup> Refer to the Timing Waveform, where n=0, 1, 2, 3, 4, 5, 6, 7.

<sup>\*\*\*</sup>In timing of "configuration read", the next DCLK rising edge should be t<sub>PD2</sub> after LE's falling edge.

<sup>\*\*\*\*</sup>The Gray Scale Clock period must be 50% duty cycle when the function of GCLK multiplier is enabled.

<sup>\*\*\*\*\*</sup>Users have to leave more time than the maximum error detection time for the error detection.

Switching Characteristics (V<sub>DD</sub>=3.3V, Ta=25°C)

| Characteristics                        |                             | Symbol               | Condition                                                | Min. | Тур. | Max. | Unit |

|----------------------------------------|-----------------------------|----------------------|----------------------------------------------------------|------|------|------|------|

|                                        | SDI - DCLK ↑                | t <sub>SU0</sub>     |                                                          | 7    | -    | -    | ns   |

| o . —                                  | LE – DCLK ↑                 | t <sub>SU1</sub>     |                                                          | 10   | -    | -    | ns   |

| Setup Time                             | LE ↓ (Vsync) – GCLK         | t <sub>SU2</sub>     |                                                          | 1200 | -    | -    | ns   |

|                                        | LE ↓ - DCLK↑                | t <sub>SU3</sub>     |                                                          | 52   | -    | -    | ns   |

|                                        | DCLK↑ - SDI                 | t <sub>H0</sub>      |                                                          | 8    | -    | -    | ns   |

| Hold Time                              | DCLK↑ - LE                  | t <sub>H1</sub>      |                                                          | 10   | -    | -    | ns   |

|                                        | GCLK – LE ↓ (Vsync)         | t <sub>H2</sub>      |                                                          | 300  | -    | -    | ns   |

|                                        | DCLK - SDO                  | t <sub>PD0</sub>     | V <sub>DD</sub> =3.3V                                    | -    | 25   |      | ns   |

| Propagation Delay<br>Time              | GCLK -OUT2n*                | t <sub>PD1</sub>     | V <sub>IH</sub> =V <sub>DD</sub><br>V <sub>IL</sub> =GND | -    | 45   | -    | ns   |

|                                        | LE – SDO                    | t <sub>PD2</sub> *** | $R_{ext}=1.4K\Omega$<br>$V_{DS}=1V$                      | _    | 40   |      | ns   |

| Pulse Width                            | LE                          | t <sub>w(LE)</sub>   | $R_L=300\Omega$                                          | 16   | -    | -    | ns   |

| Command to Comma                       | ind                         | tcc                  | C <sub>L</sub> =10pF<br>C <sub>1</sub> =100nF            | 52   | -    | -    | ns   |

| Data Clock Frequenc                    | у                           | F <sub>DCLK</sub>    | C <sub>2</sub> =10µF                                     | -    | -    | 25   | MHz  |

| Gray Scale Clock Fre                   | quency****                  | FGCLK                | C <sub>SDO</sub> =10pF<br>V <sub>LED</sub> =4.0V         | -    | -    | 20   | MHz  |

| GCLK frequency<br>(when GCLK multiplie | er is enabled)              | FGCLK                |                                                          | -    | -    | 10   | MHz  |

| Min Clock(GCLK/ DC                     | LK) Pulse Width****         | t <sub>W(CLK)</sub>  |                                                          | 13   | -    | -    | ns   |

| Ratio of (GCLK freq)/                  | R <sub>(GCLK/DCL</sub>      |                      | 20                                                       | -    | -    | %    |      |

| Compulsory Error De                    | tection Operation time***** | terr-c               |                                                          | 700  | -    | -    | ns   |

| Output Rise Time of (                  | Output Ports                | toR                  |                                                          | -    | 25   | 35   | ns   |

| Output Fall Time of O                  | Output Ports                | t <sub>OF</sub>      |                                                          | -    | 25   | 35   | ns   |

| Dead Time                              |                             | tdth                 |                                                          | 300  | -    | -    | ns   |

| Dead Time (Low state                   | e)                          | tdtl                 |                                                          | 1200 | -    | -    | ns   |

<sup>\*</sup>Output waveforms have good uniformity among channels.

<sup>\*\*</sup> Refer to the Timing Waveform, where n=0, 1, 2, 3, 4, 5, 6, 7.

<sup>\*\*\*</sup>In timing of "configuration read", the next DCLK rising edge should be tPD2 after LE's falling edge.

<sup>\*\*\*\*</sup>The Gray Scale Clock period must be 50% duty cycle when the function of GCLK multiplier is enabled.

<sup>\*\*\*\*\*\*</sup>Users have to leave more time than the maximum error detection time for the error detection.

# **Test Circuit for Switching Characteristics**

### **Timing Waveform**

### **Control timing**

(1)

(2)

(3)

(4)

(5)

(6)

#### **Control Command**

|                                  | Sig  | nals Combination                               | Description                                                                    |

|----------------------------------|------|------------------------------------------------|--------------------------------------------------------------------------------|

| Command Name                     | LE   | Number of DCLK Rising Edge when LE is asserted | Action of Command                                                              |

| Stop Compulsory Error detection  | High | 1                                              | Stop compulsory LED open detection                                             |

| Data Latch                       | High | 1                                              | Serial data are transferred to the input data buffers.                         |

| VSYNC                            | High | 2                                              | Vertical Synchronal signal. Displaying frame will be updated to output channel |

| Write Configuration 1*           | High | 4                                              | Serial data are written to the configuration register 1                        |

| Read Configuration 1             | High | 5                                              | Serial data are read from the configuration register 1                         |

| Start Compulsory Error detection | High | 7                                              | Start compulsory LED open detection                                            |

| Write Configuration 2*           | High | 8                                              | Serial data are written to the configuration register 2                        |

| Read Configuration 2             | High | 9                                              | Serial data are read from the configuration register 2                         |

| Software Reset                   | High | 10                                             | Reset the behavior of MBI5251 except the value of configuration registers.     |

| Write Configuration 5*           | High | 13                                             | Serial data are written to the configuration register 5                        |

| Pre-Active                       | High | 14                                             | Pre-Active command needs to be sent before "Write Configuration" command       |

| Read Configuration 5             | High | 21                                             | Serial data are read from the configuration register 5                         |

<sup>\*</sup>Those commands can only be activated after "Confirm command"; otherwise, they will be invalid.

**Note:** When the power is on, Vsync command will be valid only after 16 times of "Data Latch" commands that have been sent in advance.

#### **Waveform of Commands**

The following figures show the waveforms of commands.

#### **Data Latch**

Note: GCLK can not stop during this command, and GCLK\_freq / DCLK\_freq >= 1/5

Data Latch command is used to latch the 16-bit shift register from SDI to internal SRAM buffer. When this command is received, the last 16 bits data before the falling edge of LE will be latched into SRAM, as shown in the above waveform, and MSB bit needs to be sent first.

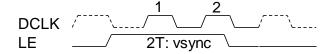

### Vertical Sync (VSYNC)

"VSYNC" command is used to update frame data on output channels (  $\overline{\text{OUT0}} \sim \overline{\text{OUT15}}$  ). There are some timing limitations between signal "LE" and "GCLK"; and please refer to the section of "Vsync Command Operation" for details.

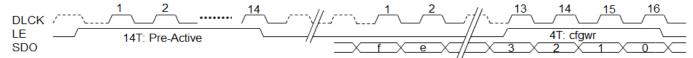

#### **Write Configuration**

Write configuration (cfgwr) command is used to program the configuration register of MBI5251. The "Pre-Active" command must be sent in advance. When this command is received, the last 16 bits data before the falling edge of LE will be latched into configuration register, as shown in the below waveforms, and MSB bit needs to be sent first.

#### Write Configuration 1

#### Write Configuration 2

#### Write Configuration 5

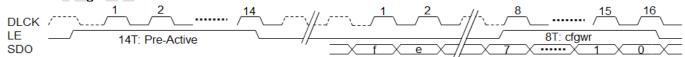

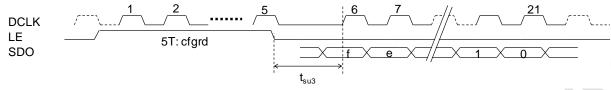

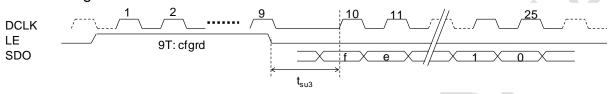

#### **Read Configuration**

Read configuration (cfgrd) command is used to read the configuration register of MBI5251. When this command is received, the 16-bit data of configuration register will be shifted out from SDO pin, as shown in the below waveforms, and MSB bit will be shifted out first.

#### Read Configuration 1

#### Read Configuration 2

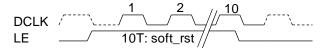

#### Read Configuration 5

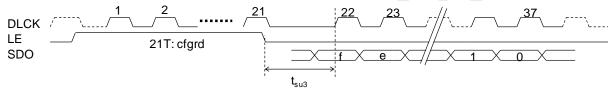

#### **Compulsory error detection**

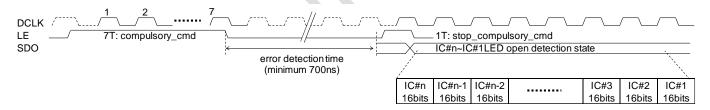

#### **Software Reset**

Software reset command makes MBI5251 go back to the initial state except configuration register value. After this command is received, the output channels will be turned off and will display again with last gray-scale value after new "Vsync" command is received.

# **Definition of Configuration Register 1**

| MSB    |         |       |   |   |   |   |   |   |   |   |   |   |   |   | LSB |

|--------|---------|-------|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| F      | Е       | D     | С | В | Α | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|        |         |       |   |   |   |   |   |   |   |   |   |   |   |   |     |

| e.g. [ | Default | Value |   |   |   |   |   |   |   |   |   |   |   |   |     |

| F      | Е       | D     | С | В | Α | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| 0      | 0       | 0     | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1   |

| Bit | Attribute      | Definition                | Value                                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|----------------|---------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F   | Read/Write     | Reserved                  | 0 (Default)                                    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| _   | D a a dAA/sita | PWM counting              | 0 (Default)                                    | PWM is forward counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| E   | Read/Write     | mode                      | 1                                              | PWM is backward counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D   | Read/Write     | LED failure induced cross | 0 (Default)                                    | Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                | elimination               | 1                                              | Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C~B | Read/Write     | Reserved                  | 00 (Default)                                   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A~8 | Read/Write     | Number of scan lines      | 000<br>001<br>010<br>011 (Default)<br>~<br>111 | 000: 1 lines<br>001: 2 lines<br>010: 3 lines<br>011: 4 lines (Default)<br>100: 5 lines<br>101: 6 lines<br>110: 7 lines<br>111: 8 lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7~6 | Read/Write     | S-PWM mode                | 00 (Default) 01 10                             | The 65536 GCLK (16-bit) PWM cycle is divided into 64 sections, each section has 1024 GCLK.  The 32768 GCLK (15-bit) PWM cycle is divided into 32 sections, each section has 1024 GCLK.  User still sends 16bit data with 1 bit 0 in LSB bits.  Ex., {15'h1234, 1'h0}.  The 16384 GCLK (14-bit) PWM cycle is divided into 32 sections, each section has 512 GCLK.  User still sends 16bit data with 2 bit 0 in LSB bits.  Ex., {14'h1234, 2'h0}.  The 8192 GCLK (13-bit) PWM cycle is divided into 16 sections, each section has 512 GCLK. User still sends 16bit data with 3 bit 0 in LSB bits. Ex., {13'h1234, 3'h0}. |

| 5~0 | Read/Write     | Current Gain              | 000,000<br>~<br>111,111 (Default)              | [000,000] 12.5%<br>~<br>[111,111] 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Default setting of configuration register is 16'h033f

# **Definition of Configuration Register 2**

| MSB    |          |       |   |   |   |   |   |   |   |   |   |   |   |   | LSB |

|--------|----------|-------|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| F      | Е        | D     | С | В | Α | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|        |          |       |   |   |   |   |   |   |   |   |   |   |   |   |     |

| e.g. D | efault ' | Value |   |   |   |   |   |   |   |   |   |   |   |   |     |

| F      | Е        | D     | С | В | Α | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| 0      | 0        | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| Bit   | Attribute    | Definition      | Value           | Function |

|-------|--------------|-----------------|-----------------|----------|

| 15    | Read/Write   | Reserved        | 0 (Default)     | Reserved |

| 13    | iteau/vviite | Neserveu        | 1               | Neserved |

| 14    | Read/Write   | Reserved        | 0 (Default)     | Reserved |

| 14    | Read/Wille   | Reserved        | 1               | Reserved |

| 13~11 | Read/Write   | Reserved        | 000 (Default)   | Reserved |

| 10    | Read/Write   | Double refresh  | 0 (Default)     | Disable  |

| 10    | inead/vviile | Double leffesii | 1               | Enable   |

| 9     | Read/Write   | GCLK multiplier | 0 (Default)     | Disable  |

| 9     | Read/Wille   | GCLK multiplier | 1               | Enable   |

| 8~5   | Read/Write   | Reserved        | 0000 (Default)  | Reserved |

| 4~0   | Read/Write   | Reserved        | 00000 (Default) | Reserved |

Default setting of configuration register is 16'h0000

# **Definition of Configuration Register 5**

| MSB |   |   |   |   |   |   |   |   |   |   |   |   |   |   | LSB |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| F   | Е | D | С | В | Α | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

#### e.g. Default Value

| F | Е | D | С | В | Α | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| Bit  | Attribute  | Definition                                      | Value                 | Function                                |

|------|------------|-------------------------------------------------|-----------------------|-----------------------------------------|

| 15~8 | Read/Write | Reserved                                        | 00000001<br>(Default) | Reserved                                |

| 7~5  | Read/Write | Open Error<br>detection<br>voltage<br>threshold | 000 (Default)         | [000] level 0<br>~<br>[111] level 7     |

| 4~0  | Read/Write | Lower ghost elimination                         | 11111 (Default)       | [00000] level 0<br>~<br>[11111] level 7 |

Default setting of configuration register is 16'h011f

### **Operation Principles**

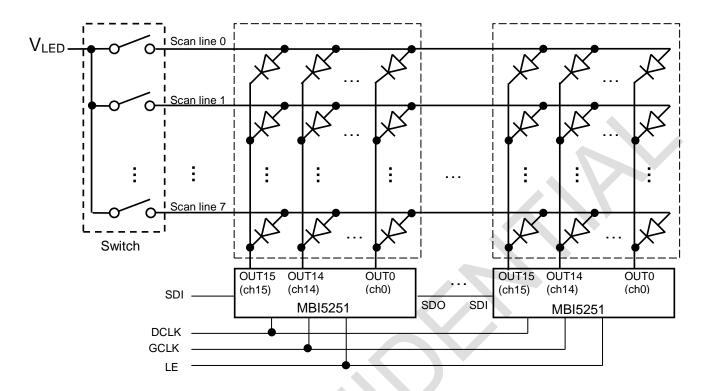

Scan type application structure

The above figure shows the suggested application structure of scan type scheme with 8 scan lines. The gray-scale data are sent by pin "SDI and SDO" with the commands formed by pin "LE" and "DCLK". The output ports from 16 channels ( $\overline{\text{OUT0}} \sim \overline{\text{OUT15}}$ ) will output the PWM result for each scan line at different time, so there must be one "Switch" to multiplex for each scan line. The switching sequence and method and the command usage is described in the application note.

#### **Constant Current**

In LED display application, MBI5251 provides nearly no variation in current from channel to channel and from IC to IC. This can be achieved by:

- 1) The maximuml current variation between channels is less than 2.5%, and that between ICs is less than ±3%

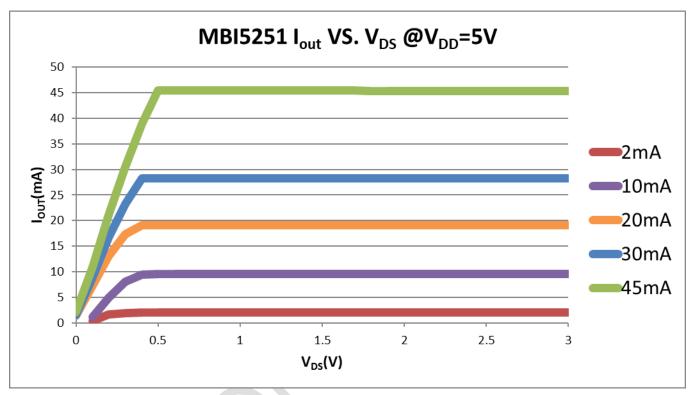

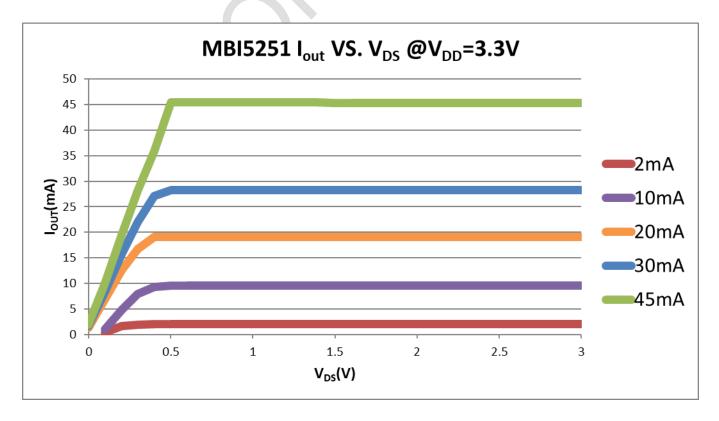

- 2) In addition, the current characteristic of output stage is flat and user can refer to the figure below. The output current can be kept constant regardless of the variations of LED forward voltages (V<sub>F</sub>). This guarantees LED to be performed on the same brightness as user's specification.

### **Setting Output Current**

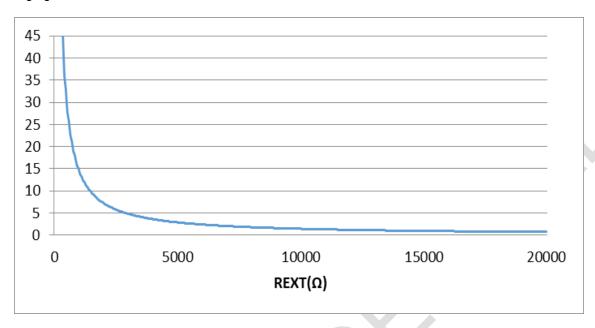

The output current ( $I_{OUT}$ ) is set by an external resistor,  $R_{ext}$ . The default relationship between  $I_{OUT}$  and  $R_{ext}$  is shown in the following figure.

Also, the output current can be calculated from the equation:

$V_{R-EXT}$ =0.61Volt

$I_{OUT} = (V_{R-EXT}/R_{ext}) \times G \times 24$

Whereas  $R_{ext}$  is the resistance of the external resistor connected to R-EXT terminal and  $V_{R-EXT}$  is its voltage. G is the digital current gain, which is set by the bit5 to bit0 of the configuration register. The default value of G is 1. For example, the output current is about 20mA when Rext=700 $\Omega$  if G is set to default value 1.

The formula and setting for G are described in next section.

### **Current Gain Adjustment**

The 6 bits (bit 5~bit 0) of the configuration register set the gain of output current, i.e., G. As total 6-bit in number, i.e., ranging from 6'b000000 to 6'b111111, these bits allow user to set the output current gain up to 64 levels. These bits can be further defined inside configuration register as follows:

| F | E | I | D | О | В | Α | 9  | 8 | 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|---|---|---|---|---|---|---|----|---|---|---|-----|-----|-----|-----|-----|-----|

| - | - | - | - |   |   | Ī | (1 | - | - |   | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 |

Bit 5 to bit 0 are DA5 ~ DA0.

The relationship between these bits and current gain G is:

$G=0.125 + (D / 63) \times 0.875$

D in the above decimal numeration can be converted to its equivalent in binary form by the following equation:

D= DA5 x 25 + DA4 x 24 + DA3 x 23 + DA2 x 22 + DA1 x 21 + DA0 x 20

In other words, these bits can be looked as 6-bit mantissa DA5~DA0

For example:

G = 0.5

$D = (0.5 - 0.125) / 0.875 \times 63 = 27$

D in binary form would be:

D = 27

=0 x 25 + 1 x 24 + 1 x 23 + 0 x 22 + 1 x 21 + 1 x 20

The 6 bits (bit 5~bit 0) of the configuration register are set to 6'b011011

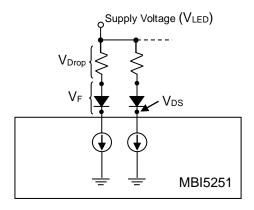

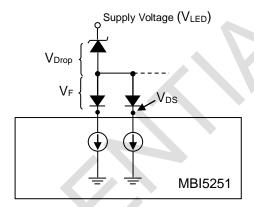

### **LED Supply Voltage (VLED)**

MBI5251 is designed to operate with  $V_{DS}$  ranging from 0.4V to 1.0V (depending on  $I_{OUT}=2\sim45$ mA) considering the package power dissipating limits.  $V_{DS}$  may be higher enough to make  $P_{D}$  (act)  $>P_{D}$  (max) when  $V_{LED}=5$ V and  $V_{DS}=V_{LED}-V_{F}$ , in which  $V_{LED}$  is the load supply voltage. In this case, it is recommended to use the lowest possible supply voltage or to set an external voltage reducer,  $V_{DROP}$ .

A voltage reducer lets  $V_{DS}=(V_{LED}-V_F)-V_{DROP}$ .

Resistors or Zener diode can be used in the applications as shown in the following figures.

### **Switching Noise Reduction**

LED drivers are frequently used in switch-mode applications which always behave with switching noise due to the parasitic inductance on PCB. To eliminate switching noise, refer to "Application Note for 8-bit and 16-bit LED Drivers-Overshoot".

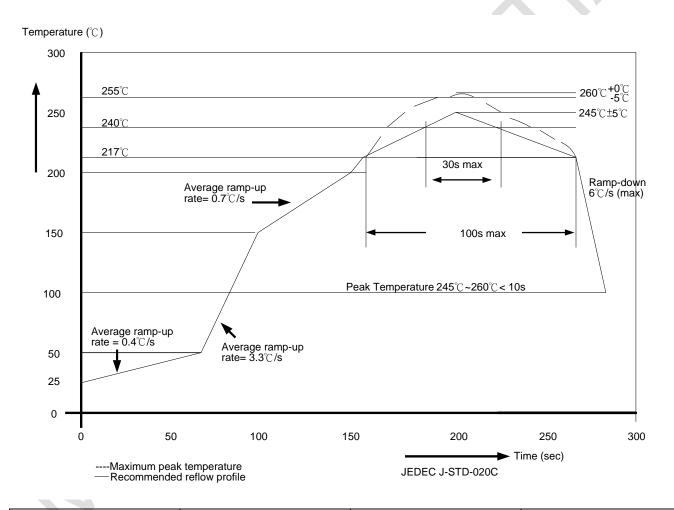

### Soldering Process of "Pb-free & Green" Package Plating\*

Macroblock has defined "Pb-Free & Green" to mean semiconductor products that are compatible with the current RoHS requirements and selected 100% pure tin (Sn) to provide forward and backward compatibility with both the current industry-standard SnPb-based soldering processes and higher-temperature Pb-free processes. Pure tin is widely accepted by customers and suppliers of electronic devices in Europe, Asia and the US as the lead-free surface finish of choice to replace tin-lead. Also, it adopts tin/lead (SnPb) solder paste, and please refer to the JEDEC J-STD-020C for the temperature of solder bath. However, in the whole Pb-free soldering processes and materials, 100% pure tin (Sn) will all require from 245°C to 260°C for proper soldering on boards, referring to JEDEC J-STD-020C as shown below.

For managing MSL3 Package, it should refer to JEDEC J-STD-020C about floor life management & refer to JEDEC J-STD-033C about re-bake condition while IC's floor life exceeds MSL3 limitation.

| Package Thickness | Volume mm³<br><350 | Volume mm³<br>350-2000 | Volume mm³<br>≧2000 |

|-------------------|--------------------|------------------------|---------------------|

| <1.6mm            | 260 +0 °C          | 260 +0 °C              | 260 +0 °C           |

| 1.6mm – 2.5mm     | 260 +0 °C          | 250 +0 °C              | 245 +0 °C           |

| ≧2.5mm            | 250 +0 °C          | 245 +0 °C              | 245 +0 °C           |

<sup>\*</sup>Note: For details, please refer to Macroblock's "Policy on Pb-free & Green Package".

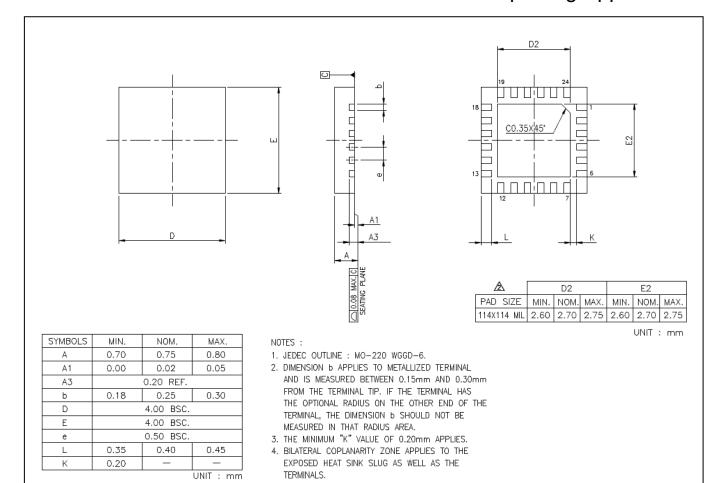

### **Package Outline**

MBI5251GP Outline Drawing

MBI5251GFN Outline Drawing

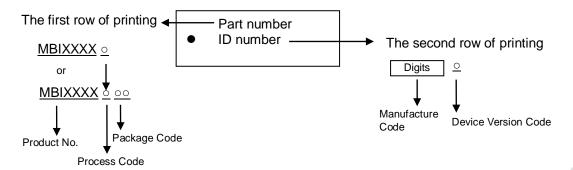

### **Product Top Mark Information**

**Product Revision History**

| Advance Information Version | Devise Version Code |

|-----------------------------|---------------------|

| V0.01                       | Т                   |

**Product Ordering Information**

| Product Ordering Number* | RoHS Compliant Package Type | Weight (g) |

|--------------------------|-----------------------------|------------|

| MBI5251GP-T              | SSOP24L-150-0.64            | 0.11       |

| MBI5251GFN-T             | QFN24L-4*4-0.5              | 0.0379     |

<sup>\*</sup>Please place your order with the "product ordering number" information on your purchase order (PO).

#### **Disclaimer**

Macroblock reserves the right to make changes, corrections, modifications, and improvements to their products and documents or discontinue any product or service. Customers are advised to consult their sales representative for the latest product information before ordering. All products are sold subject to the terms and conditions supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. Macroblock's products are not designed to be used as components in device intended to support or sustain life or in military applications. Use of Macroblock's products in components intended for surgical implant into the body, or other applications in which failure of Macroblock's products could create a situation where personal death or injury may occur, is not authorized without the express written approval of the Managing Director of Macroblock. Macroblock will not be held liable for any damages or claims resulting from the use of its products in medical and military applications.

Related technologies applied to the product are protected by patents. All text, images, logos and information contained on this document is the intellectual property of Macroblock. Unauthorized reproduction, duplication, extraction, use or disclosure of the above mentioned intellectual property will be deemed as infringement.